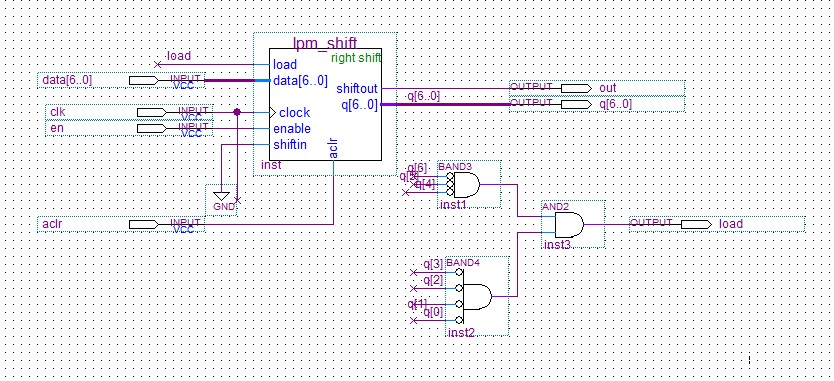

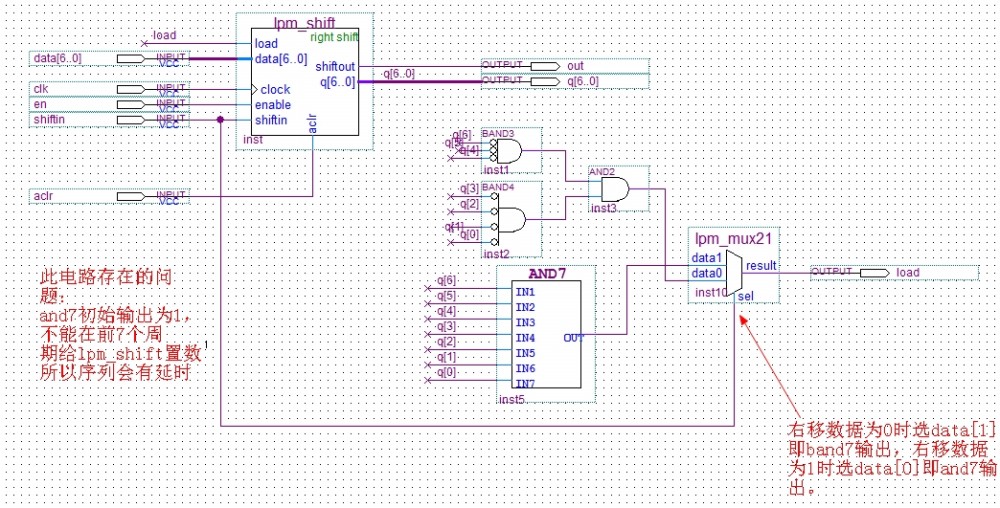

一、序列发生器电路图

基本部件全部采用lpm定制。

lpm_shift为右移位寄存器,为了直观的仿真和在数码管上显示,

用左移位寄存器是更好的选择。

lpm_shift是LPM定制的7位右移位寄存器,带串入串出和并入并出。

load端为置数端,当load端为1时,寄存器置数,并行输出为data[6..0],当load无效,即load为0时,右

移位输出,具体过程如下:假设data[6..0]为 1110010,右移入0,则序列右端(q[0])依次被弹出

(shiftout即为q[0]端,即q[0]端产生串行输出序列),序列为 0100111。

当移入7个0时,经band7到load端输入为1,则寄存器置数,q[6..0]重新置数为data[6..0],开始下一轮

序列。注:q[6..0]是data[6..0]依次右移0的序列,并非所求序列并行输出,如果要接数码管,需再接一

个串入并出移位寄存器。

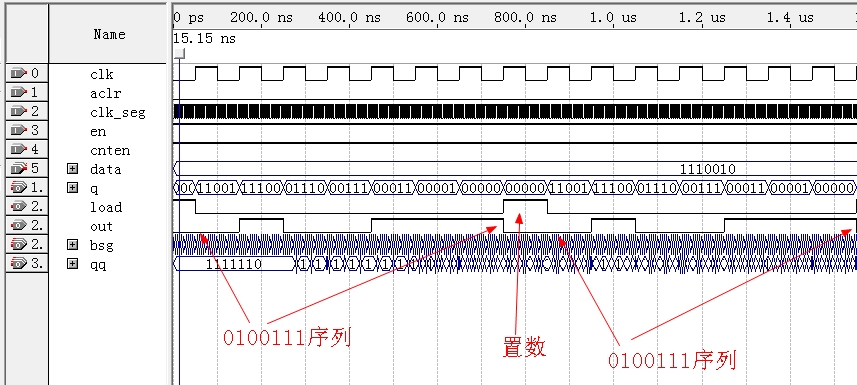

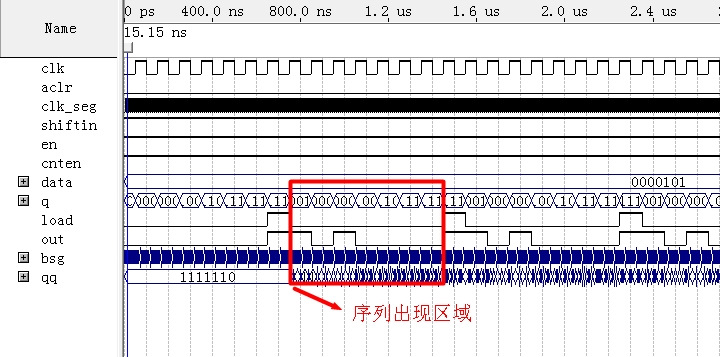

仿真测试如下:

正确生成了0100111序列。

关于band:

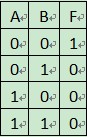

band2真值表:

即只有输入全为0时输出才为1,这样就会出现问题,考虑序列0000011(生成序列为1100000,更一般的情况:生成序列最后一位位0时,此时应考虑移入1而不是0),当右移入2个0时,就已经是全0了,此时经band7输出为1,即load开始置数,不能得到预定序列:

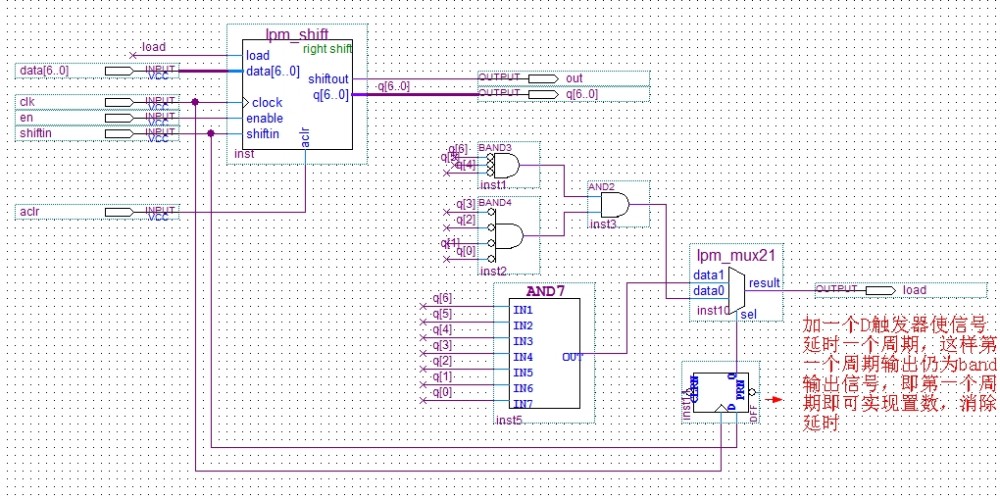

修改电路图如下:

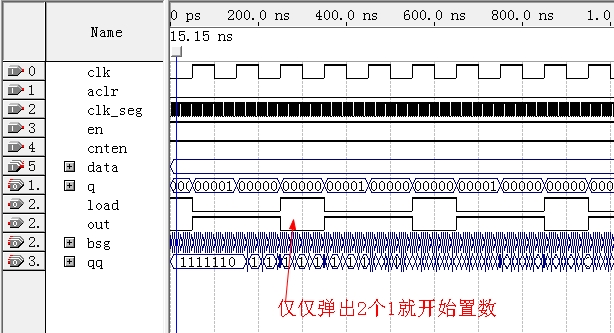

仿真结果:

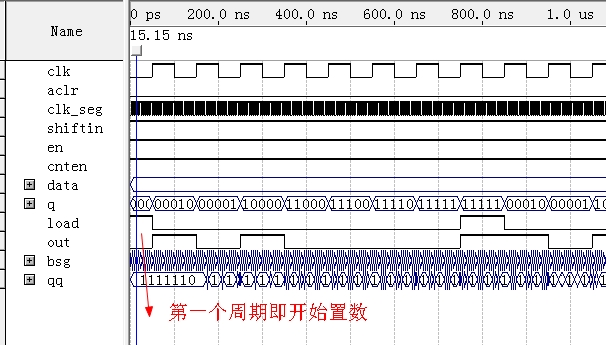

消除置数延时的修改电路:

修改后电路仿真结果:

发表回复