上周四器件实验,做四分频器,完全不懂是个什么玩意,后来从同学那里抄来了电路图,用7474连好,到是实现了功能,可是为什么就可以分频呢?数字设计没学好的人真心搞不懂,看来基础很重要。

今天好好画了下波形,大概能明白一点了。

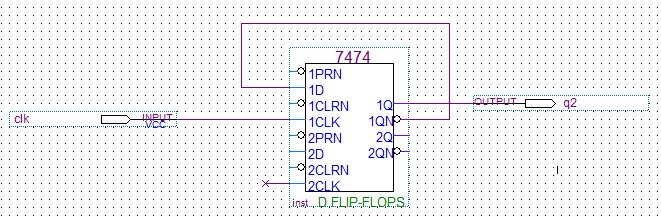

下图是一个二分频的电路,用7474实现

二分频电路

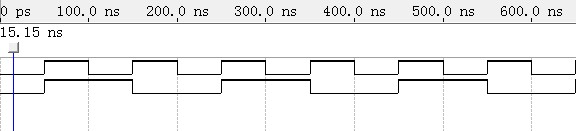

其实,输出端Q只能在CLK时钟上升沿改变,也就是只要使数据输入电平在时钟上升沿到来之前与上一个时钟上升沿不同就行了,至于中间怎么变化无所谓了,但是,在接一个数据输入端,并且控制信号的频率,那样就太麻烦了。观察要实现的功能:

二分频波形

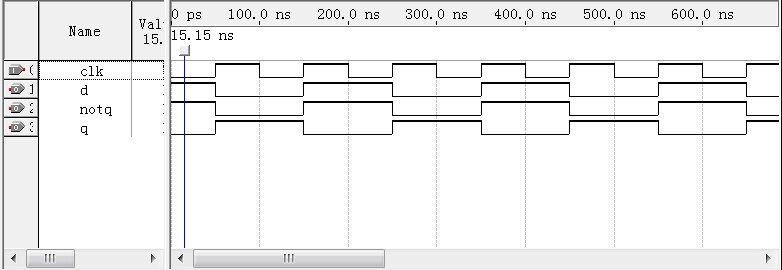

如果数据输入正好与输出端Q相反,上面的图依然成立,而Q‘ 正好是与Q相反的,既然这样,把数据输入端和Q’ 端连在一起不就解决问题了?

下图显示了clk,d,q'和q的波形,可见,d,q'同步,d,q'和q刚好相反,实现了二分频:

二分频波形

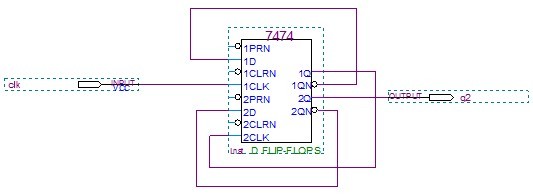

二分频的信号在分频一次,就是四分频了,依此类推,可以实现8分频,16分频....

四分频电路

发表回复