花了很长时间,走了很多弯路,终于完成了模405计数器的设计。

首先设计一个具有同步置数,异步清零,同步使能,进位输出的10进制计数器:

这里用了lpm定制,注意选择模10.

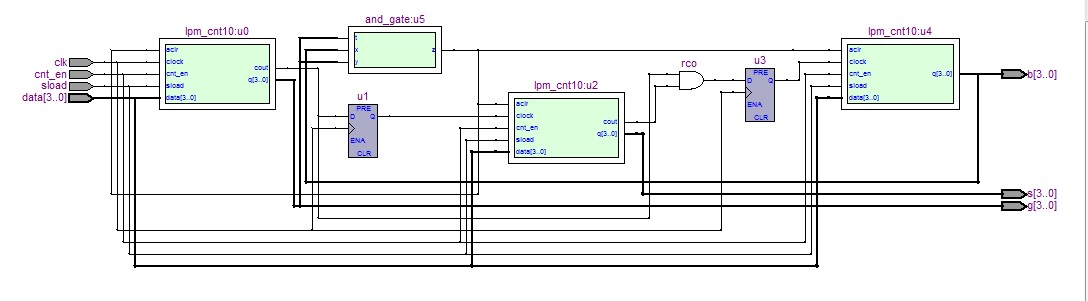

顶层设计:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity cnt405 is

port(clk,cnt_en,sload:in std_logic;

data:in std_logic_vector(3 downto 0);

b:out std_logic_vector(3 downto 0);

s:out std_logic_vector(3 downto 0);

g:out std_logic_vector(3 downto 0));

end cnt405;

architecture rtl of cnt405 is

component lpm_cnt10

PORT

(

aclr : IN STD_LOGIC ;

clock : IN STD_LOGIC ;

cnt_en : IN STD_LOGIC ;

data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sload : IN STD_LOGIC ;

cout : OUT STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

);

end component;

component dff --D触发器元件声明

port(d,clk:in std_logic;

q:out std_logic);

end component;

component and_gate --声明与门

port(x,y,t:in std_logic;

z:out std_logic);

end component;

--内部连线

signal rco_ten:std_logic;

signal rco_ten2:std_logic;

signal rco_ten3:std_logic;

signal q0:std_logic;

signal q00:std_logic;

signal q_ten:std_logic_vector(3 downto 0);

signal q_ten2:std_logic_vector(3 downto 0);

signal q_ten3:std_logic_vector(3 downto 0);

signal q2:std_logic;

signal rco:std_logic;

--元件例化,端口映射

begin

u0:lpm_cnt10 port map(q2,clk,cnt_en,data,sload,rco_ten,q_ten);

u1:dff port map(rco_ten,clk,q0); --进位延迟一个时钟周期

u2:lpm_cnt10 port map(q2,q0,cnt_en,data,sload,rco_ten2,q_ten2);

rco

开始使用了置数的方法,但是发现由于百位到9时才会有时钟上升沿,因此,到405后百位不会按预期置数,而是保持4,所以会看到这样的计数序列:403,404,405,400,401,402,403,404,405,400,401......

所以选择异步清零是不错的办法。

RTL调试:

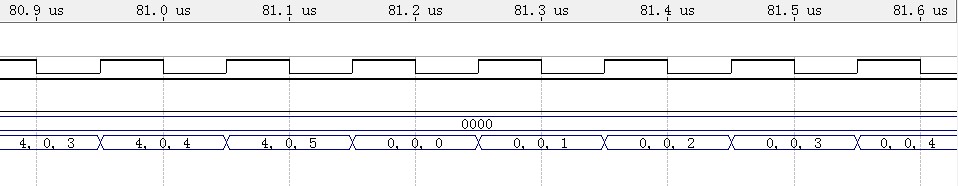

仿真结果:

发表回复